Carte CPLD

La carte CPLD qui gère le décodage des signaux des codeurs optiques fixés sur les moteurs, a été développée par un ami (Mr Béber pour ne pas le nommer) dans le but de décoder les signaux en quadrature des encodeurs, et de compter les impulsions. Elle est basée sur un CPLD Xilinx XC95144XL. Je sais qu’il existe des composants tout fait qui réalisent ce décodage mais je préférais avoir ma propre carte pour apprendre à bien utiliser un cpld en conditions réelles. Un autre avantage est le fait de pouvoir coder une liaison série entre l’arduino et cette carte au lieu d’une liaison parallèle très couteuse en pattes coté arduino (il y en a très peu de disponibles, c’est un atmega168 de 28 broches PDIP)

Voici le principe de fonctionnement :

La structure interne

Chaque codeur est relié au CPLD qui viens décoder les signaux en quadrature. Une fois décodés ces signaux sont comptés avec un compteur 12 bits (pourquoi 12 bits ? parce que c’est la taille max qui peut rentrer dans ce CPLD) dont la valeur peut être récupérée par la MAE (Machine à Etats) qui gère la communication série. Il y a aussi un registre 8 bits de sortie, permettant de contrôler 8 sorties numériques au besoin. Tout le système de configuration qui est géré par la boite noire qu’est la MAE, fonctionne sur le principe de registres adressés (pour acceder à un registre on spécifie son adresse) dans lesquels on vient écrite les valeurs de configuration. Il y a actuellement 4 registres :

- TCON : Timer configuration. Permet d’activer ou désactiver les timers T0 et T1, ainsi que de choisir si une RAZ du timer est faite sur lecture de sa valeur.

- R1 : Registre de sortie. Permet d’écrire de controler 8 bits en sortie sur un port du CPLD.

- T0 : Accès en lecture / écriture à la valeur du Compteur 0

- T1 : Accès en lecture / écriture à la valeur du Compteur 1

Communication Série

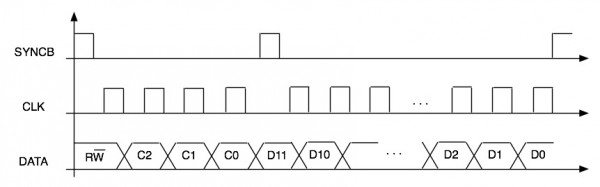

La communication série est de type maître / esclave pour plus de simplicité : le microcontroleur peut être le seul initiateur d’une communication entre lui est le CPLD. Les signaux de contrôle de la communication (SYNCB et CLOCK) sont exclusivement contrôlés par le microcontroleur. Le principe de communication est le suivant : une première trame de 4 bits est envoyée au CPLD pour spécifier l’adresse du registre (3bits) auquel on veut accéder ainsi que le mode lecture ou écriture (1bit). En suivant, une trame de 12bit est envoyée dans le cas d’une écriture, ou lue dans le cas d’une lecture. Le microcontroleur contrôle l’horloge qui séquence la communication série. Au total, vu mon implémentation une lecture ou une écriture dans un registre prend environ 12us. Pendant chaque trame, le signal SYNCB doit être au niveau bas pour indiquer qu’une communication est en cours. Il est au niveau haut au repos. Cela permet d’éviter d’attraper tout les parasites qui passent sur la ligne quand il n’y a pas de communication et d’être certain de la synchronisation du début de transmission entre le CPLD et le microcontroleur.

Voici une image montrant un exemple d’écriture dans le CPLD :